# Heterogeneous computing to enable highest level of safety

Ramanujan Venkatadri Automotive Innovation Center, Infineon Technologies

| 1 | Challenges to address next generation automotive systems     | 3  |

|---|--------------------------------------------------------------|----|

| 2 | Exponential increase in workload specific compute            | 5  |

| 3 | How to secure the future connected vehicle?                  | 7  |

| 4 | How to achieve higher levels of autonomy?                    | 9  |

| 5 | How to address the new EE architecture challenges            | 11 |

| 6 | Introduction to next generation AURIX TC4xx microcontrollers | 13 |

| 7 | Example application use case                                 | 29 |

| 8 | Summary                                                      | 31 |

| 1 | Challenges to address next generation automotive systems     | 3  |

|---|--------------------------------------------------------------|----|

| 2 | Exponential increase in workload specific compute            | 5  |

| 3 | How to secure the future connected vehicle?                  | 7  |

| 4 | How to achieve higher levels of autonomy?                    | 9  |

| 5 | How to address the new EE architecture challenges            | 11 |

| 6 | Introduction to next generation AURIX TC4xx microcontrollers | 13 |

| 7 | Example application use case                                 | 29 |

| 8 | Summary                                                      | 31 |

|   |                                                              |    |

# Challenges with developing autonomous, electric and connected Vehicle

Connected, Autonomous Electric Mobility

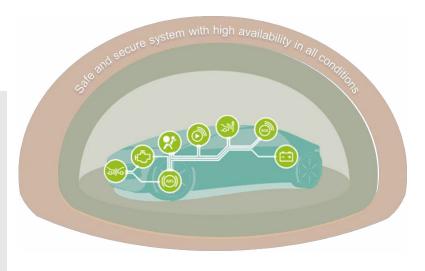

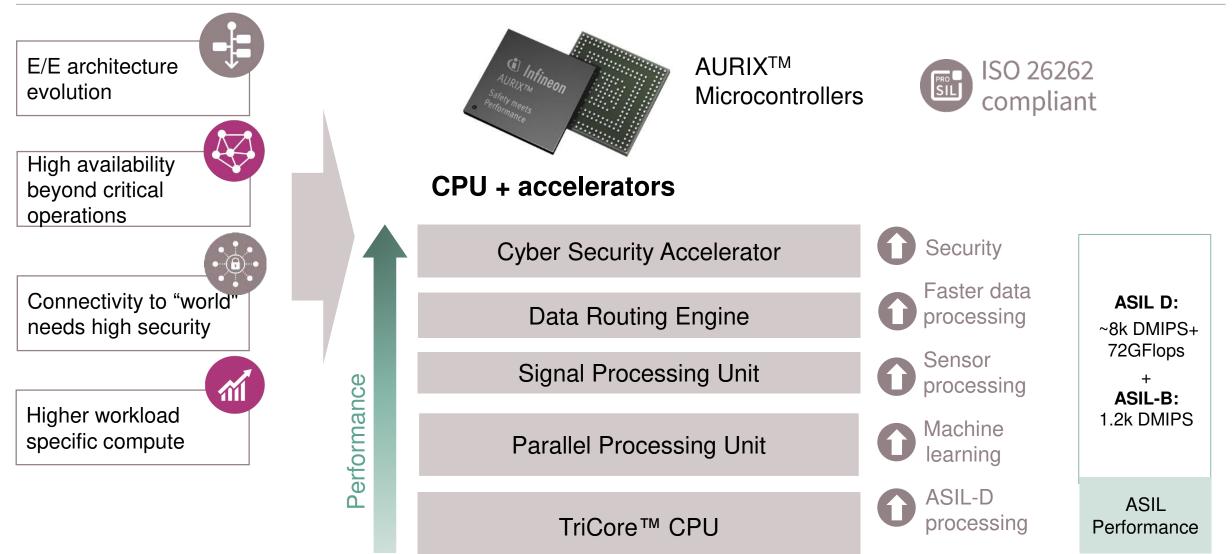

E/E architecture evolution

High availability beyond critical operations

Connectivity to "world" needs high security

Evolving technologies (ex: Battery, Sensing, and AI) Higher workload specific compute

| 1 | Challenges to address next generation automotive systems     | 3  |

|---|--------------------------------------------------------------|----|

| 2 | Exponential increase in workload specific compute            | 5  |

| 3 | How to secure the future connected vehicle?                  | 7  |

| 4 | How to achieve higher levels of autonomy?                    | 9  |

| 5 | How to address the new EE architecture challenges            | 11 |

| 6 | Introduction to next generation AURIX TC4xx microcontrollers | 13 |

| 7 | Example application use case                                 | 29 |

| 8 | Summary                                                      | 31 |

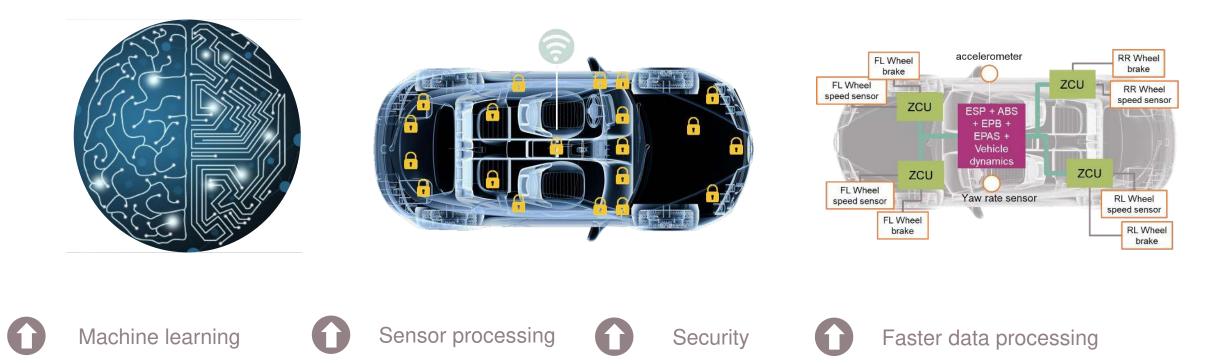

# Increase in demand for workload specific compute

Artificial Intelligence & sensor specific workload accelerators

Faster security accelerators for authenticity & Integrity

3

Higher connectivity interfaces with low latency data processing

|   | Challenges to address next generation automotive systems     | 3  |

|---|--------------------------------------------------------------|----|

| 2 | Exponential increase in workload specific compute            | 5  |

| 3 | How to secure the future connected vehicle?                  | 7  |

| 4 | How to achieve higher levels of autonomy?                    | 9  |

| 5 | How to address the new EE architecture challenges            | 11 |

|   |                                                              | 10 |

| 6 | Introduction to next generation AURIX TC4xx microcontrollers | 13 |

|   | Example application use case                                 | 29 |

| 8 | Summary                                                      | 31 |

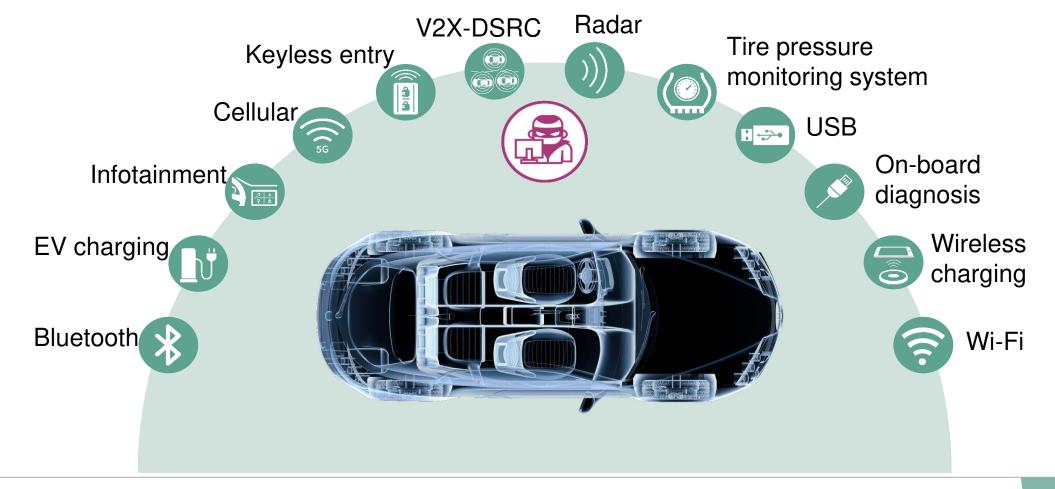

The connected mobility : How to secure the future vehicle?

### Every connection in the car is a potential entry point for an attacker...

| 1 | Challenges to address next generation automotive systems     | 3  |

|---|--------------------------------------------------------------|----|

| 2 | Exponential increase in workload specific compute            | 5  |

| 3 | How to secure the future connected vehicle?                  | 7  |

| 4 | How to achieve higher levels of autonomy?                    | 9  |

| 5 | How to address the new EE architecture challenges            | 11 |

| 6 | Introduction to next generation AURIX TC4xx microcontrollers | 13 |

| 7 | Example application use case                                 | 29 |

| 8 | Summary                                                      | 31 |

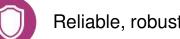

**High Availability** | Ensure high availability beyond critical operations; a safe and secure system, that operates in all conditions

Fail-Operational | Mitigate potentially hazardous effects by ensuring critical operations in the event of a failure

Fail-Safe | in the event of a failure, system enters safe state

Lower levels (ADAS, <L2)

System enters safe mode

Reliable, robust, safe, secure

System continues safety critical tasks

Higher levels (AD,  $\geq$ L3+)

High availability in all conditions

Fail operational + highly available

Systei

| 1 | Challenges to address next generation automotive systems     | 3  |

|---|--------------------------------------------------------------|----|

| 2 | Exponential increase in workload specific compute            | 5  |

| 3 | How to secure the future connected vehicle?                  | 7  |

| 4 | How to achieve higher levels of autonomy?                    | 9  |

| 5 | How to address the new EE architecture challenges            | 11 |

| 6 | Introduction to next generation AURIX TC4xx microcontrollers | 13 |

| 7 | Example application use case                                 | 29 |

| 8 | Summary                                                      | 31 |

# E/E architecture : How to support next generation E/E architectures?

nfineon

| 1 | Challenges to address next generation automotive systems     | 3  |

|---|--------------------------------------------------------------|----|

| 2 | Exponential increase in workload specific compute            | 5  |

| 3 | How to secure the future connected vehicle?                  | 7  |

| 4 | How to achieve higher levels of autonomy?                    | 9  |

| 5 | How to address the new EE architecture challenges            | 11 |

| 6 | Introduction to next generation AURIX TC4xx microcontrollers | 13 |

| 7 | Example application use case                                 | 29 |

| 8 | Summary                                                      | 31 |

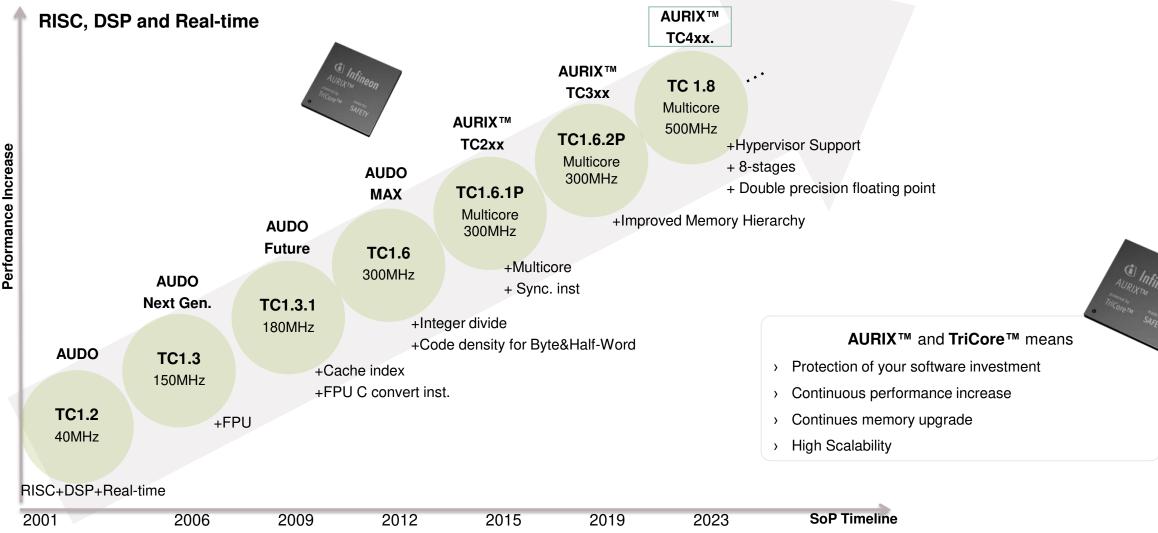

# Infineon AURIX<sup>™</sup> - the most dependable microcontroller platform

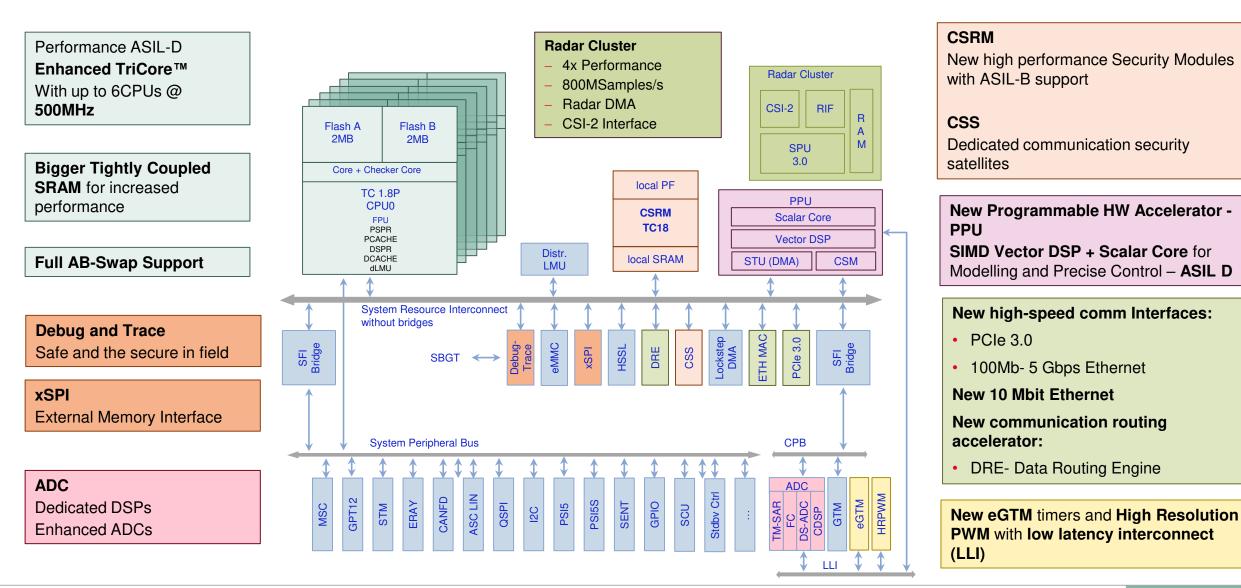

# AURIX<sup>™</sup> TC4x defines the next controller standard for safe & secure ECUs with strong networking capabilities

### **Higher Performance**

- New 500MHz TriCore™ 1.8

- PPU: Private scalar core + 512bit wide vector unit with up to 72 GOPS

- SPU3: High-performance radar processing subsystem

- A/D Converter sub-system

with integrated DSPs

- Data Routing Engine for CAN Ethernet - Mem communication

### Safety and Security

- AURIX™ meets ISO26262-2018 ASIL D safety standard

- CSRM: high-performance security module with private CPU, memories and crypto accelerators

- **CSS**: Distributed crypto and hash engines for secure CAN/Ethernet communication

- Security according to ISO 21434 standard planned

### **Freedom From Interference**

- Hardware isolation at core and peripheral level

- TriCore™ 1.8 with **up to eight** VMs per core and Hypervisor

- Ultra-fast context switching

- Enhanced memory protection for cores and virtual machines

- Fine-granular access protection to peripherals

- Isolated DMA protection

### **Rich connectivity**

- > Up to 2x **5GBit Ethernet** incl. Bridge

- Accelerated MACsec support by HW accelerator in CSS and application SW driver

- 4x10/100MBit Ethernet supporting 10Base-T1S standard

- > Up to 2x 8GBit/s PCle 3.0 1x lane

- Up to 20x CAN-FD

# AURIX<sup>™</sup> TC4x Architecture Enhancements compared to AURIX<sup>™</sup> TC3x

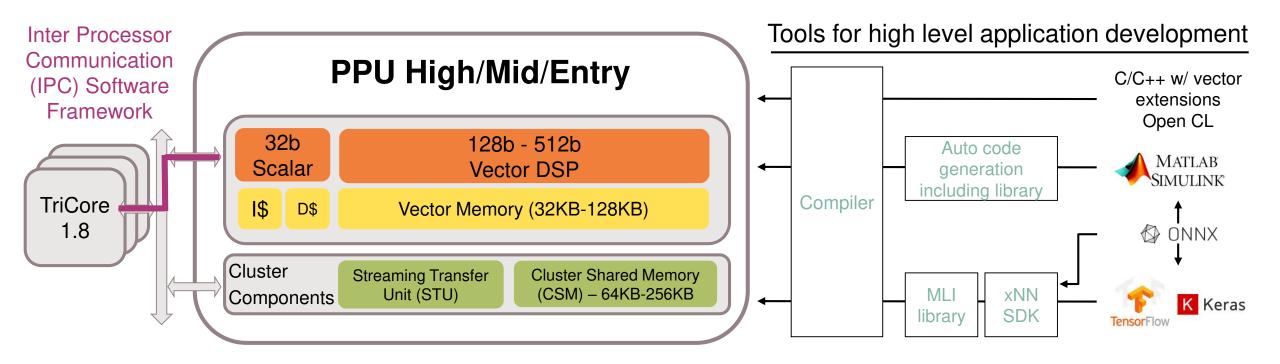

# Workload specific compute – Machine Learning

- Scalable PPU EV71FS in TC4x portfolio

- > SIMD vector DSP co-processor

- Matrix operation acceleration & data processing

- > Neural network based algorithms

- > High speed control implementation

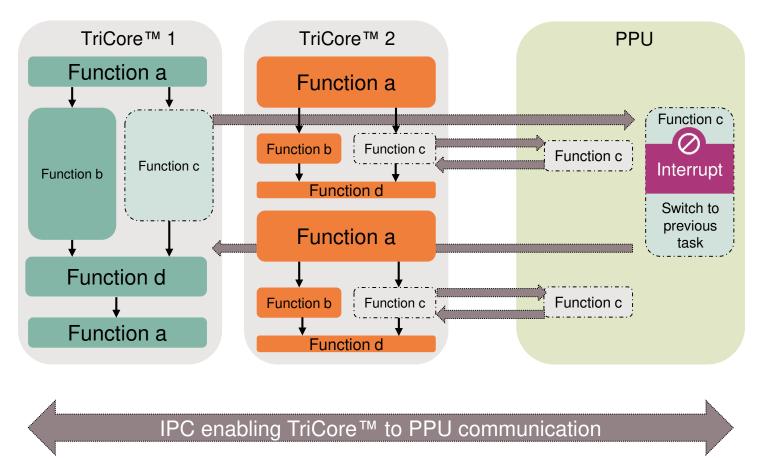

# Inter processor communication between Tricore<sup>™</sup> and PPU

- PPU compute resource will be shared between multiple host CPUs

- Outsourcing of functions into PPU enables speed up of applications tasks

- Middleware is integrated into basic software using complex device driver

- Single level of interruption (priority scheme) is considered

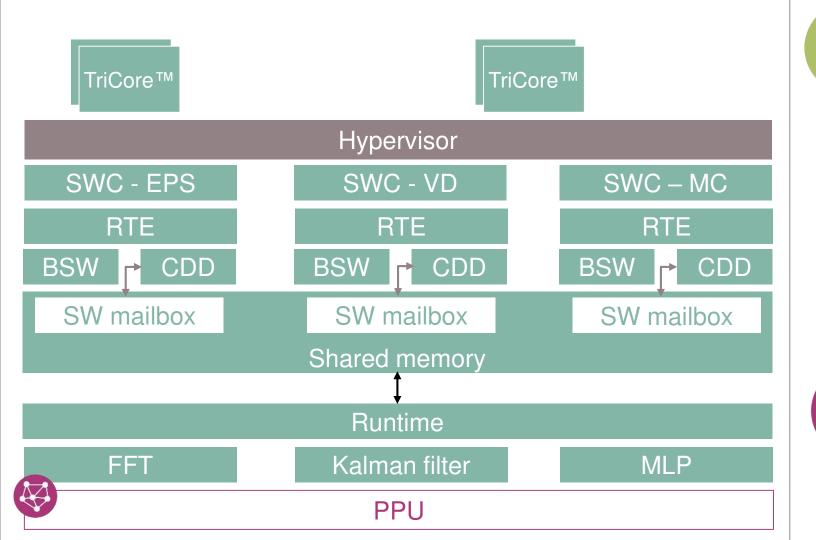

# Example: PPU middleware communication with AUTOSAR stack on Tricore™

Example: AUTOSAR Environment

- Three physically isolated AUTOSAR stacks

- Each communicates with PPU using dedicated complex device driver (CDD)

- CDD communicates with middleware on PPU

PPU middleware detects requests and executes

Software on PPU does not differentiate its clients

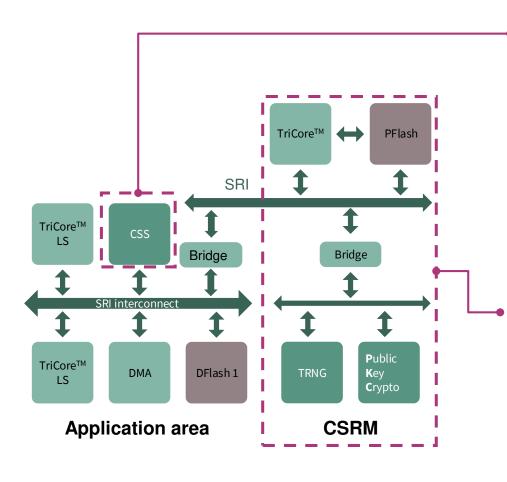

# Security: Hardware acceleration and secure connection to the internet world

# Security cluster of AURIX<sup>™</sup> TC4x increases throughput by parallel computation and supports upcoming new security standards

### New AURIX<sup>™</sup> TC4x security cluster

### Cyber security satellite (CSS) for parallel computation

- Parallelization of HW accelerators in service provider to application area to avoid performance bottlenecks by

- > Increasing throughput

- Minimizing latency

- > 21 individual channels to be used by application (compared to one channel in TC3x)

- > Providing freedom of interference for domain / zone controllers

### Cyber security real-time module (CSRM) for performance increase

- → Upgrade to TriCore<sup>™</sup> 1.8

- > providing ~5-15x more performance vs. TC3x HSM

- CSRM as trusted secure HW environment supporting new security standards (e.g. ISO 21434)

- Private Program Flash within CSRM which supports individual security SW updates independent of application core

- > Enables realization of multiple security use cases for wide ranging applications

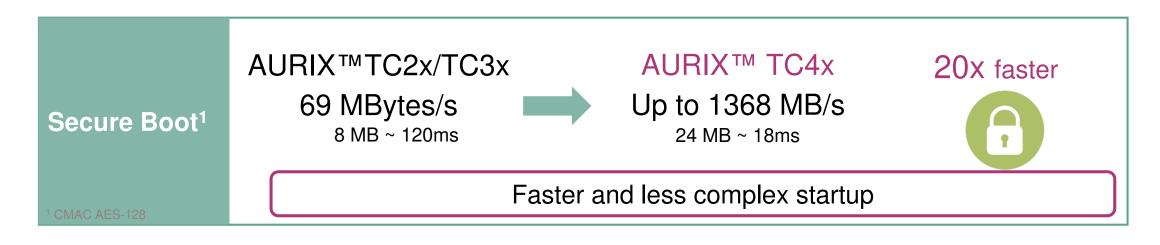

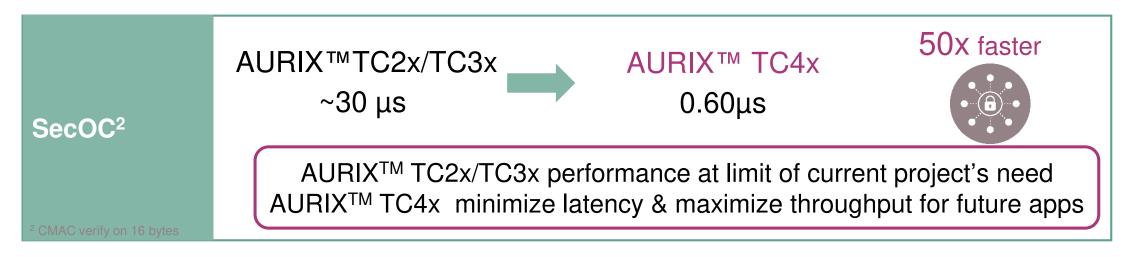

# Security use cases require significantly enhanced performance

### Security use cases covered by AURIX<sup>™</sup> TC4x

#### Enabled by SW on CSRM and HW on CSS/PKC/TRNG

- Secure boot

- > Debugger protection

- > Immobilizer

- > Tuning protection

- > Secure Update

- > Secure (key-) storage

- > Component protection

- > Key management

- Feature Activation

- Remote Diagnosis Car Access

(OBD)

- Plug & Charge OBC (ISO 15118)

Flight Recorder / Secure Odometer

- Device Attestation

- Connection to external Service Provider

#### In-vehicle network (IVN) & V2x (e.g. vehicle to cloud) security

- > E/E COM (message) observation:

- Intrusion Detection System (IDS)

- > E/E COM (message) filtering:

- > Intrusion Detection Prevention System (IDPS)

- > Firewall: Feasible by HW filters in MAC and SW

- COM Message Security (e.g. CAN(FD)/Ethernet):

- Authenticated Encryption with Associated Data (AEAD); Authentication with Associated Data (AAD)

- Combined modes are supported in CSS

### Why is the new security cluster needed?

**Minimize latency & maximize throughput** as an increasing number of security use cases are expected for the future

Supporting new Security standards (e.g. ISO 21434)

**Enable SOTA use cases**, which require secure and safe distribution of SW updates from cloud or within IVN

**Serve AEAD and AAD solutions**, which are expected to gain importance in the future: authentication of >50% and encryption of >15-20% of all IVN messages

Security : Significant performance improvement for AURIX<sup>™</sup> TC4xx

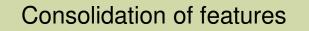

# Freedom from interference : Safe hardware isolation

# Hardware Isolation to separate ASIL and non ASIL applications

Need for Isolation

Example: Zone

controller

Cross-domain

functions in a

single ECU

Upto 6 per vehicle

- Reduce number of ECUs

- > Enhance computing power

- Combine multiple applications with different OS on one MCU

### Separation of applications

- > Safety: cannot mix safe & unsafe SW

- Security

∃ ∃ ∃ • • •

5

Liability: keep SW from partners separate

### Flexibility

- > Enable collaboration from multiple partners

- > Separate startup/ shutdown of application

- > Independent updates to fix/ upgrade: i.e. OTA

- > Monetization: Activate or deactivate features

Introducing Virtual Machines (VM)

- > Isolation containers

- Isolates application execution & control path

- One ECU could need upto 30

- Need to be safe, secure

& easy to use

# Virtual ECUs deployment using Hypervisor

### AURIX<sup>™</sup> TC4xx TriCore

Advanced isolation features at CPU level

# Access Protection Unit (APU)

Provides isolation features at the peripherals

### **Virtual Machines**

With complete AUTOSAR stack & assignment of own peripherals

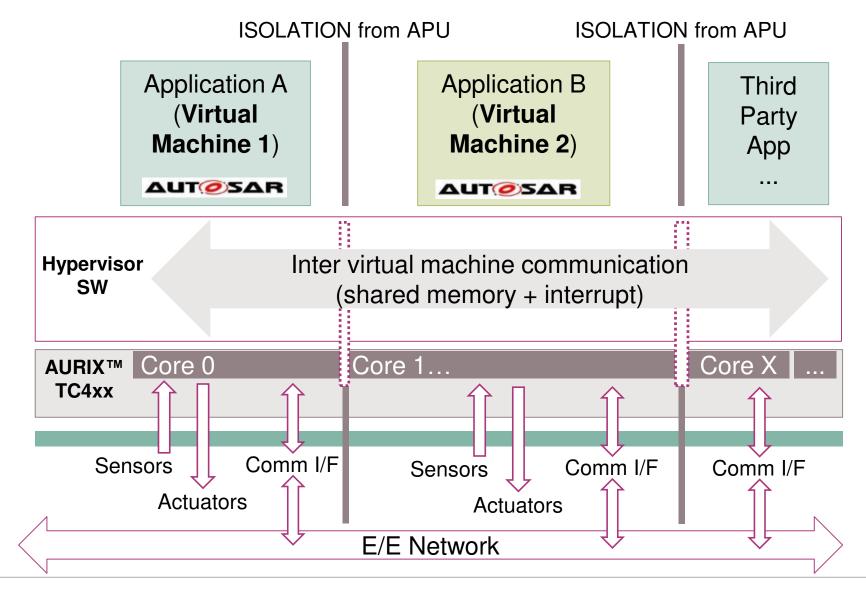

# Rich connectivity and low latency data routing

# Feature set deep dive: Rich connectivity TC4xx meets the latency and ethernet performance challenges

Damper

### Challenge:

Latency when sharing real time data i.e. wheel sensor between zone controllers

### Challenge:

Ethernet bridge performance & redundancy for safety critical application in daisy chain & ring topologies

### TC4xx DRE/CRE routing accelerators:

- Reduces SW processing load of data transmission

- > Increase performance and throughput

- > by reducing routing latency and jitter

- > Use-cases covered:

- Packet forwarding CAN←→CAN

- Packet formatting and encapsulation CAN  $\leftarrow \rightarrow$  ETH

- Packet storage CAN→Memory

### TC4xx Ethernet MACs and Ethernet bridge:

- > High-speed Ethernet with TSN support

- Combo MAC with 100Mbps and 10BaseT1s support

- > Ethernet bridge with filter and parser capabilities

Reduces communication load on CPUs and enables safety critical real time communication

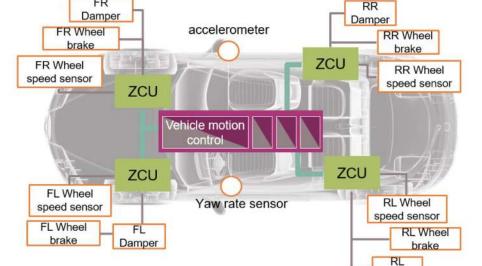

# Comprehensive ethernet and CAN connectivity and feature set to address wide variety of future IVN demands

### 2 x 5 Gbps MAC

Supported speeds:

- > 100Mbps (MII,RMII, RGMII)

- > 1Gbps(RGMII, SGMII)

- > 2.5Gbps (SGMII)

- > 5Gbps (SGMII)

### 4 x 10/100 Mbps MAC

Supported speeds:

- > 100Mbps (MII, RMII)

- > 10Mbps (3 Pin Transceiver) Supported topologies:

- > point-to-point (100M)

- > Bus (10M)

Ethernet MAC Features

- > Quality of service: provides queues for frames

- > Classification: applies rules to inbound packets

- > **TSN**: provides functions to achieve real time behavior

- > Intrusion detection: supports detection of anomalies

- > **Bridge**: support fast forwarding of frames

### **CSS - Security Accelerator**

Supports security algorithms for

- MACsec

- ) IPsec

- > D/TLS

- SecOC (PDU level)

### 20 x CAN-FD nodes and routing engine

- CAN-to-CAN frame routing across all 20 CAN channels

- > CAN-to-Memory frame routing

- CAN-to-Ethernet routing (IEEE:1722 support)

- > Multi-cast up to 4 destinations

- > Intrusion Detection support

- > Virtualization support

# Software Ecosystem

#### Last generation re-use plus Enabling development with new IP support of new computing IP plus increased safety support > TriCore<sup>™</sup> compiler: PPU libraries and auto code generation: > TASKING, Hightec, WindRiver, > Synopsys, TASKING GHS > AURIX TC4x hardware support package Compiler Software > MATLAB / Simulink > PPU compiler: development and > Synopsys, TASKING, Hightec > Safety software package (in discussion) debugger kits Startup tests and failure checks recommended > Debugger and test tools: > iSYSTEM, Lauterbach, PLS, in safety manual **Optional CDSP software toolchain** Synopsys Synopsys Increased MCAL offering and **Enablement of pre-AUTOSAR** providers incl. hypervisor silicon development **MCAL** and Virtual > Proprietary MCAL with ISO26262:2018 compliance > **Provider:** Synopsys **AUTOSAR** prototype for IPs incl. new COM Ips (PCIe, DRE, 10BaseT1s)

- Modelling of key AURIX TC4x HW features

- > Full debug and analysis support

- Interfaces to Simulink, SABER, CANoe, etc.

- > Hypervisor implementation

- > EB, ETAS, Opensynergy, SysGo, Greenhills

### > SW stack integration providers:

- Vector, Elektrobit, Siemens, ETAS

- Security SW: Vector, ESCRYPT, ISS, EB

|   | Challenges to address next generation automotive systems     | 3  |

|---|--------------------------------------------------------------|----|

| 2 | Exponential increase in workload specific compute            | 5  |

| 3 | How to secure the future connected vehicle?                  | 7  |

| 4 | How to achieve higher levels of autonomy?                    | 9  |

| 5 | How to address the new EE architecture challenges            | 11 |

| 6 | Introduction to next generation AURIX TC4xx microcontrollers | 13 |

| 7 | Example application use case                                 | 29 |

| 8 | Summary                                                      | 31 |

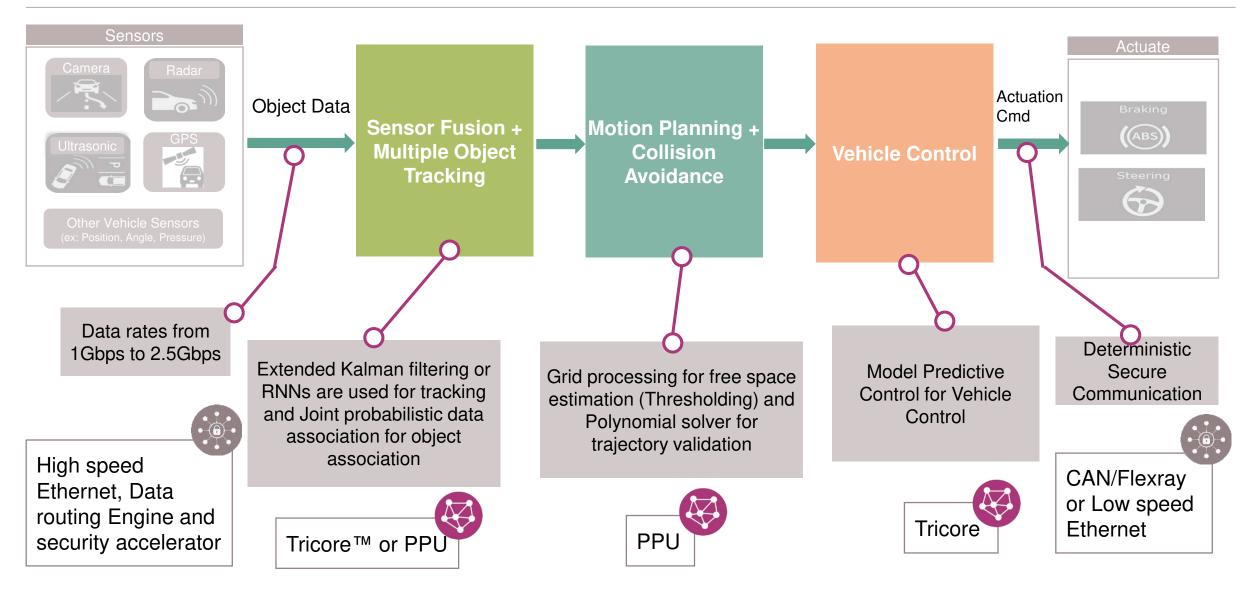

# Example ADAS use case : Autonomous L1/L2 Sensor Fusion

| 8 | Summary                                                      | 31 |

|---|--------------------------------------------------------------|----|

| 7 | Example application use case                                 | 29 |

| 6 | Introduction to next generation AURIX TC4xx microcontrollers | 13 |

| 5 | How to address the new EE architecture challenges            | 11 |

| 4 | How to achieve higher levels of autonomy?                    | 9  |

| 3 | How to secure the future connected vehicle?                  | 7  |

| 2 | Exponential increase in workload specific compute            | 5  |

|   | Challenges to address next generation automotive systems     | 3  |

|   |                                                              |    |

# AURIX<sup>™</sup> TC4xx Heterogeneous SoC architecture enabling highest level of safety for automotive applications

Summary : AURIX<sup>™</sup> TC4xx enables heterogeneous computing with industry leading functional safety concept

AURIX<sup>™</sup> TC4xx offers tremendous computational power boost compared to previous generation deploying new applications with complex computing needs

Optimized SoC with high speed connectivity, data routing engine, hypervisor for isolation to enable next generation EE architectures

Scalable and flexible Parallel Processing Unit (PPU) enables affordable artificial intelligence with its high performance SIMD architecture

Holistic functional safety concept with improved safety mechanisms, Security cluster supporting security standards and with significantly enhanced performance

AURIX<sup>™</sup> TC4xx offers a scalable platform from low end to high devices enabled with rich software ecosystem to support the next generation of mobility

# Part of your life. Part of tomorrow.