# Aquabolt-XL: Samsung HBM2-PIM with in-memory processing for ML accelerators and beyond

Jin Hyun Kim, Shin-haeng Kang, Sukhan Lee, Hyeonsu Kim, Woongjae Song, Yuhwan Ro, Seungwon Lee, David Wang, Hyunsung Shin, Bengseng Phuah, Jihyun Choi, Jinin So, YeonGon Cho, JoonHo Song, Jangseok Choi, Jeonghyeon Cho, Kyomin Sohn, Youngsoo Sohn, Kwangil Park, and Nam Sung Kim

Samsung Electronics

ACKNOWLEDGMENT: We have partners and customers that we discussed and shared many ideas with. Nevertheless, unlike companies that cannot open due to NDA issue, we must mention who helped with HW, SW, and system enabling. Hsien-Hsin Sean Lee, Liu Ke, from Facebook for AXDIMM and Yun Wu, Arun Vr Varadarajan Rajagopal, Matt Klein, Kumar Subramany, Henley Liu, from Xilinx for U280-PIM

### Contents

### **1. Processing-in-Memory Concept**

### 2. Aquabolt-XL HBM2-PIM

- Hardware Architecture

- Software Stack and Programming Model

### 3. Aquabolt-XL system evaluation

- Aquabolt-XL with GPU

- Aquabolt-XL with Xilinx FPGA (U280)

### 4. Next PIM solution

- LPDDR5-PIM

- AXDIMM, DIMM-PIM

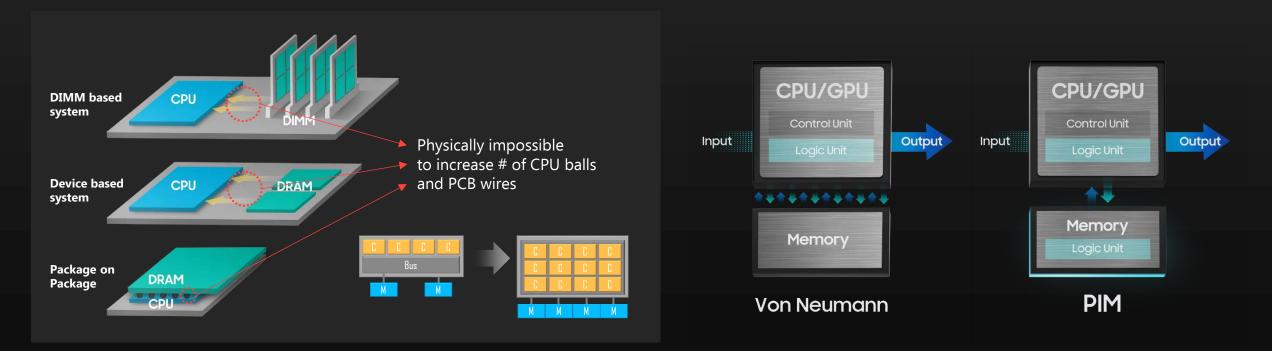

# Using PIM to overcome memory bottleneck

- Although various bandwidth increase methods have been proposed, it is physically impossible to achieve a breakthrough increase.

Limited by # of PCB wires, # of CPU ball, and thermal constraints

- PIM has been proposed to improve performance of bandwidth-intensive workloads and improve energy efficiency by reducing computing-memory data movement.

### **Re-thinking PIM and Re-architecting memory hierarchy**

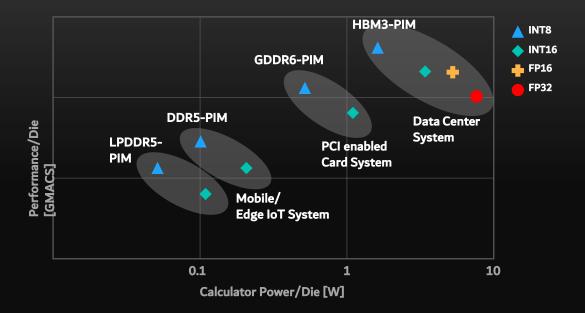

- PIM provides high ops/second and low power [Survey and Benchmarking of Machine Learning Accelerators] not only extension of commodity but also various hierarchical optimized solutions have been proposed.

- Closes performance gap and delivers energy-efficient solutions [Hotchips '16, Jin Hyun Kim, Samsung] - PIM in LLC/Near memory/DIMM

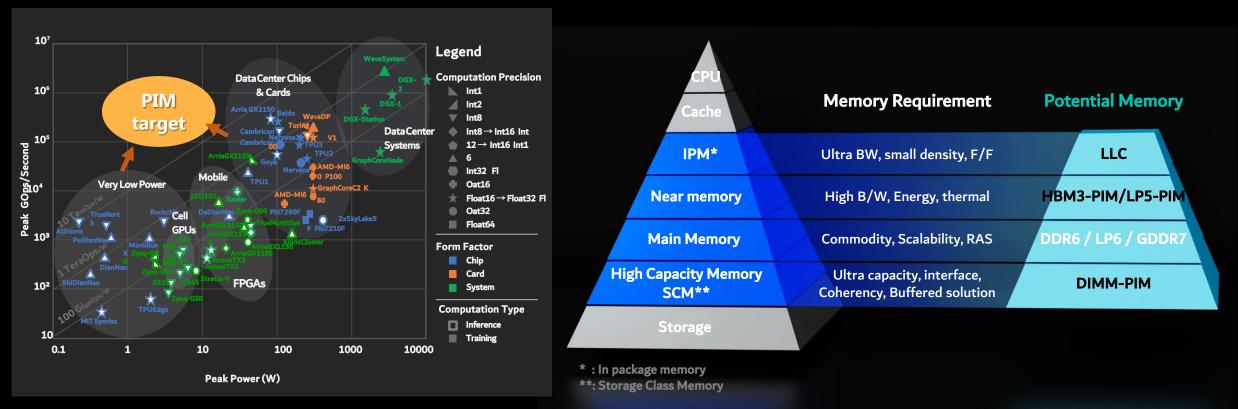

# Aquabolt-XL, System-Level 1<sup>st</sup> PIM memory

- The first demonstrator vehicle of PIM is based on HBM2 Aquabolt, which is used in leading edge AI and HPC systems. ۲

- PCU\* is integrated with a memory core on a single chip to enable parallel processing and minimize data movement. ۲

- Improves the performance and energy efficiency of the system with in-DRAM processing ٠ - Performance : Utilize up to 4× higher in-DRAM bandwidth by multi-bank parallel operation

\*: Programmable Computing Unit

HBM

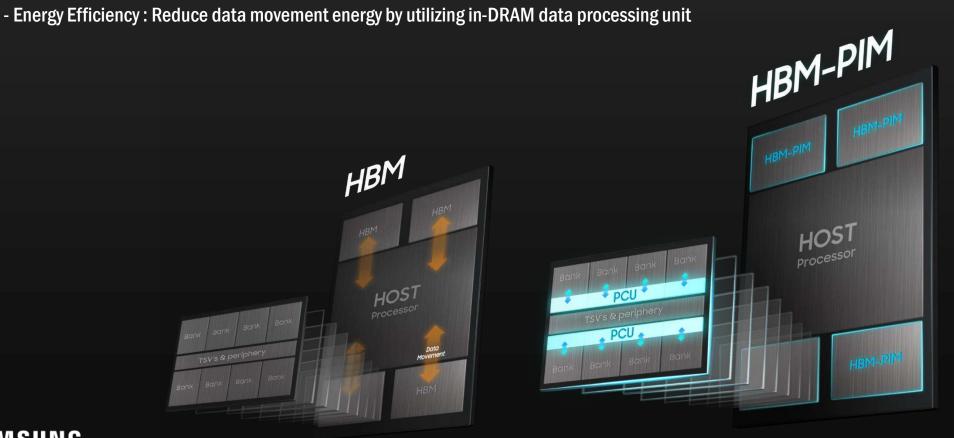

# **Aquxbolt-XL, System-Level Evaluation**

- XPUs are highly performant for compute-bound workloads but expend significant time and energy processing memory-bound workloads with low arithmetic intensity.

- PIM naturally complements xPUs for optimal system balance and performance per watt for memory-bound workloads - Speech Recognition, Natural Language Translation, Recommendation

- Aquabolt-XL is able to deliver over 2X system performance while reducing energy consumption by more than 70%.

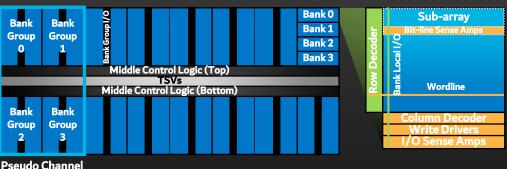

# Aquabolt HBM2 (High Bandwidth memory)

- HBM2 provides high memory bandwidth (more than 256GB/s) by 3D-stacking up to eight DRAM dies

- DRAM dies communicate with the buffer die using through silicon vias (TSVs)

- Buffer die is connected to a host xPU with silicon interposer

- An HBM2 stack of eight DRAM dies (8-Hi) has two 64-bit channels per die for a total of 16 pseudo channels and a width of 1024 bits

- Each pair of two DRAM dies share host memory bus In 8-Hi HBM, which doubles the memory capacity, not bandwidth compared to 4-Hi HBM

Pseudo Channe

System in Package (SiP)

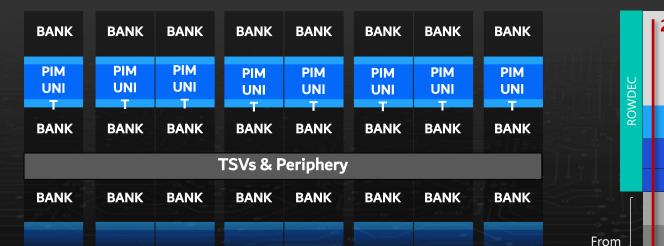

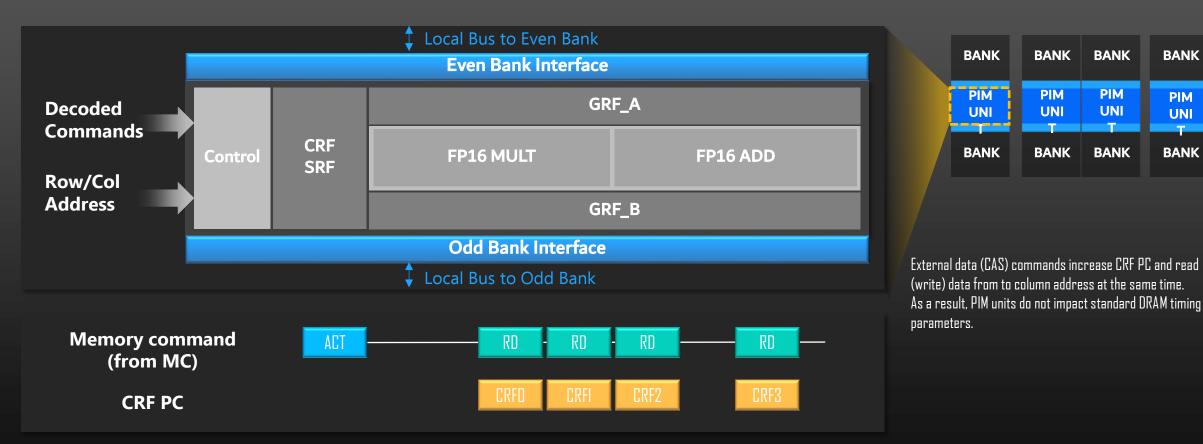

# **Aquabolt-XL HBM2-PIM Architecture**

- Place a programmable PIM execution unit at the I/O boundary of a bank based on HBM2

- Exploit bank-level parallelism: access multi banks/FPUs in a lockstep manner

- Support both standard HBM and Aquabolt-XL modes for versatility

**HBM** Core Die

- Minimize engineering cost of re-designing DRAM core to support PIM

- Maintain the same form-factor and timing parameters as baseline Aquabolt product

- Facilitate drop-in replacement of JEDEC-specification compliant Aquabolt HBM2 with Aquabolt-XL HBM-PIM for any system

- DRAM RD/WR command triggers execution of a PIM instruction in PIM mode

- Preserving deterministic DRAM timing

#### Bank

Registers

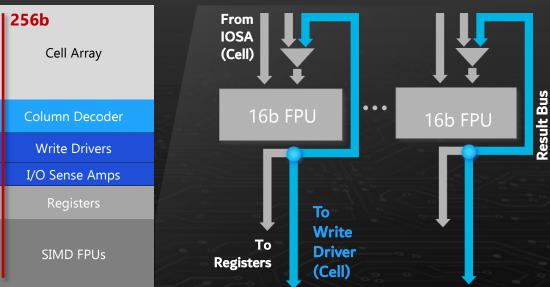

# **PIM Microarchitecture**

• Consist of three major components with DRAM local bus interface:

- A 16-lane FP16 SIMD FPU array: a pair of 16 FP16 multipliers and adders

- Register files: Command, General, and Scalar register files (CRF, GRF, and SRF)

- A PIM unit controller (fetch and decode, controls pipeline signals, forward)

# **PIM Instruction-Set Architecture**

- Supports RISC-style 32-bit instructions.

- Three Instruction types (Total 9 instructions)

- 3 Control flow: NOP, JUMP, EXIT

- 2 Data transfer: MOV, FILL

- 4 Arithmetic: ADD, MUL, MAC, MAD

- JUMP instruction:

- Zero-cycle static branch: supports only a preprogrammed numbers of iterations

- Operand type: Vector Register(GRF\_A, GRF\_B), Scalar Register(SRF), and Bank Row Buffer

- DRAM commands decide where to retrieve data from DRAM for PIM arithmetic operations

| Туре            | Operation | Operand (SRC0) | Operand (SRC1) | Result (DST) | # of combinations |  |

|-----------------|-----------|----------------|----------------|--------------|-------------------|--|

|                 | ADD       | GRF, BANK, SRF | GRF, BANK, SRF | GRF          | 40                |  |

| Arithmetic      | MUL       | GRF, BANK      | GRF, BANK, SRF | GRF          | 32                |  |

| Aritnmetic      | MAC       | GRF, BANK      | GRF, BANK, SRF | GRF_B        | 14                |  |

|                 | MAD       | GRF, BANK      | GRF, BANK, SRF | GRF          | 28                |  |

| Data            | MOVE      | GRF, BANK      |                | GRF, SRF     | 24                |  |

| Transfer        | FILL      | GRF, BANK      |                | GRF, BANK    | 12                |  |

|                 | NDP       |                |                |              | 1                 |  |

| Control<br>Flow | JUMP      |                |                |              | 1                 |  |

|                 | EXIT      |                |                |              | 1                 |  |

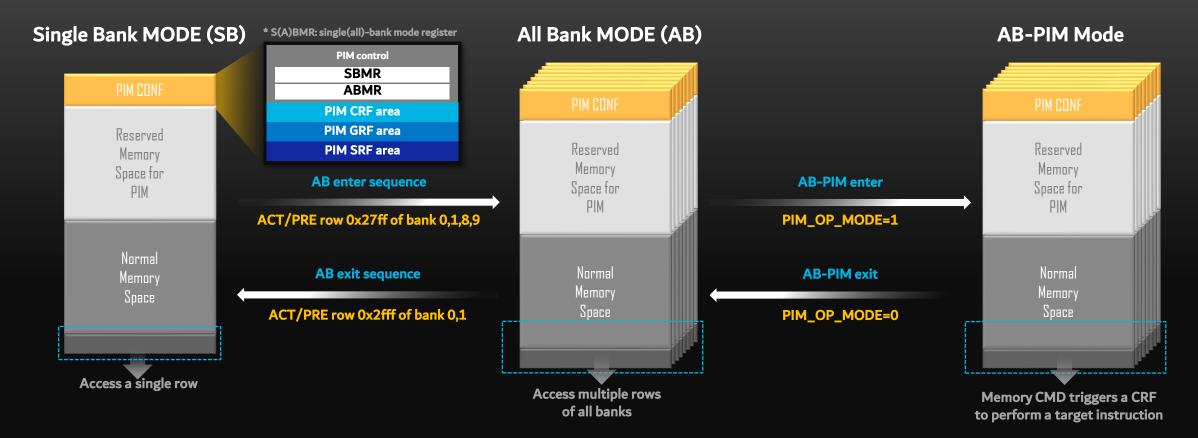

### **PIM Operation mode**

- Three execution mode: Single Bank (SB), All Bank (AB), and All Bank PIM (AB-PIM)

- Use sequence of standard JEDEC-standards compatible DRAM commands for mode transition

- Using PIM configuration area

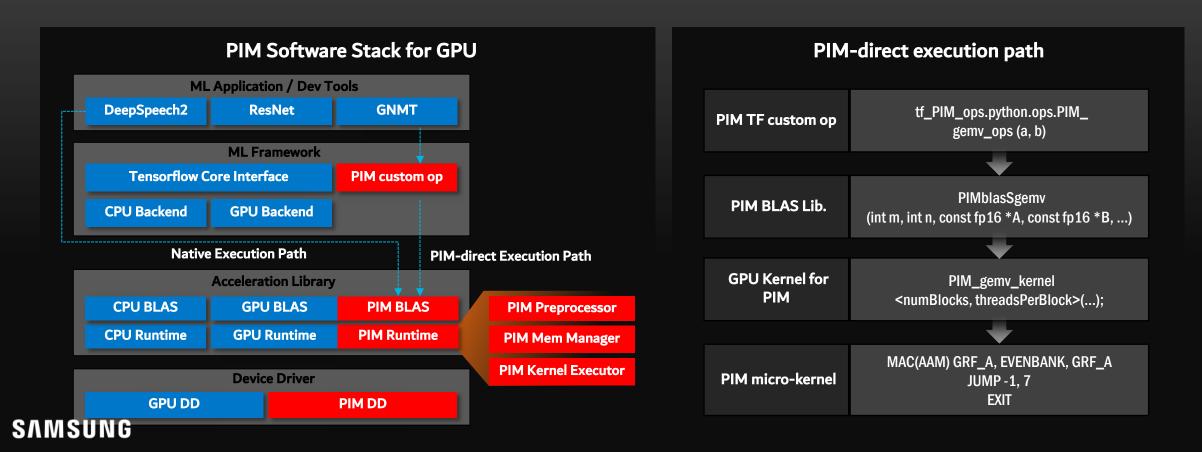

# **PIM Software Stack**

- Developed PIM SW stack to allow users to run unmodified source code based on ML frameworks (TensorFlow and Pytorch)

- Supports two execution path

- Native execution path: Automatically offload PIM-friendly TF operations, does not require any modification of application source code.

- PIM-direct execution path: Explicitly call custom PIM-specific TF operations

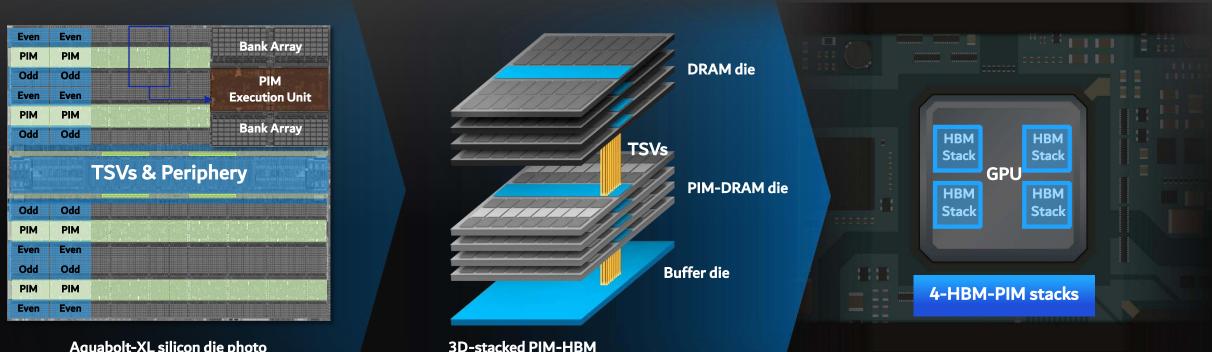

# **Chip Implementation and Integration with systems**

- Implemented PIM by modifying a commercial HBM2 design (Aquabolt). Resulting HBM-PIM device codenamed Aquabolt-XL ٠

- Integrated the fabricated Aquabolt-XL with an unmodified GPU and Xilinx FPGA ٠

- Validated fabricated HBM-PIM in system with unmodified HBM controller

- Off-chip and on-chip PIM compute bandwidth is 1.23 TB/s and 4.92 TB/s, respectively.

Aquabolt-XL silicon die photo

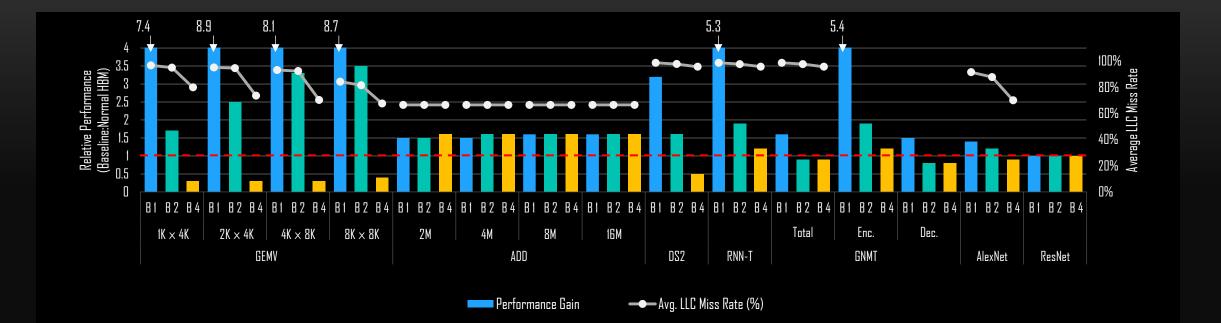

### **Evaluation – Performance**

- Evaluated performance and energy efficiency of HBM-PIM-based system

- Performance Gain: 11.2× (Microkernel GEMV) and 3.5× (Speech Recognition Application)

- Energy Efficiency: Reduces the energy per bit transfer by 3.5× (overall energy efficiency of the system running the applications by 3.2×)

Micro benchmarks: vector-matrix multiplication (GEMV), element-wise addition (ADD)

- End-to-end applications: 3 NLP apps (DS2, RNN-T, and GNMT), 2 CV apps (AlexNet and ResNet)

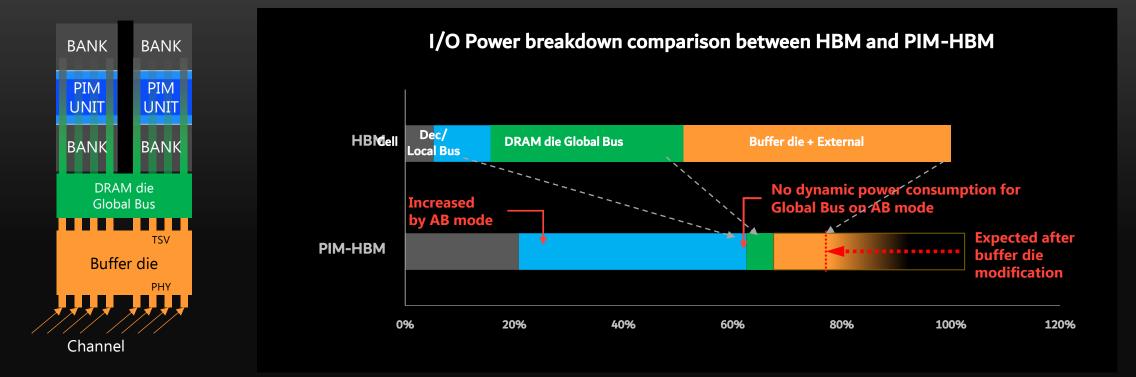

# **Evaluation – Power/Energy**

- HBM-PIM consumes only 5.4% higher power compared to the HBM.

- In HBM-PIM, multiple PIM execution units operate concurrently

- power consumption of DRAM internal components (gray and blue) increases proportionally, but

- power consumption of internal global I/O bus (green) and I/O PHYs (orange) considerably decreases.

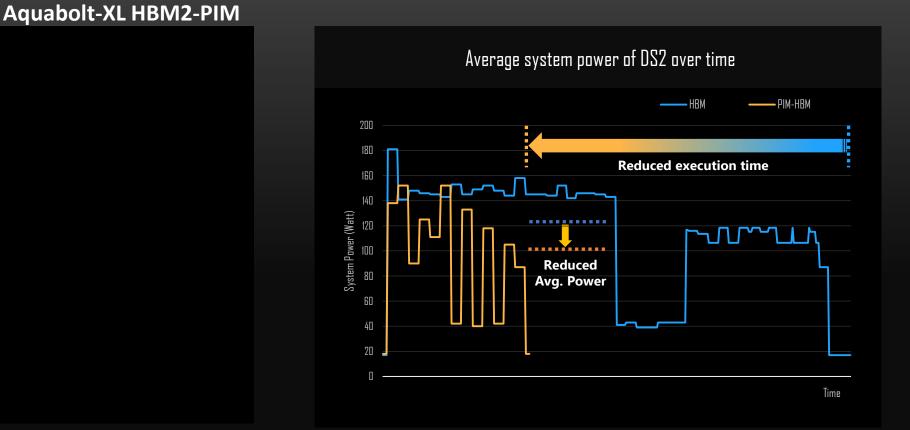

### **Evaluation – system power analysis, demonstration**

- Evaluate the functionality and performance of real-life systems using a tensor flow implementation of Deepspeech2 - Compare ASR trends, statistics of inference latency and word/character error rate

- HBM-PIM improves energy efficiency by shorter execution time and lower average power consumption

### Aquabolt HBM2

# Xilinx Alveo U280: Evaluation setup

- For fair comparison, we created two separate FPGA projects:

1) Baseline with default memory-controller setting

2) PIM-accelerated logic with custom memory-controller setting

- Applied different memory controller configurations to each FPGA project - Memory controller configuration for PIM doesn't affect baseline performance

- Guarantee the correct order of PIM-related memory commands and no auto pre-charge

- Designed baseline and PIM logic to utilize maximum HBM bandwidth

### **PIM Evaluation Architecture**

2-HBM-PIM stacks

XILINX.

**U280 FPGA**

# Xilinx Alveo U280: Evaluation Results

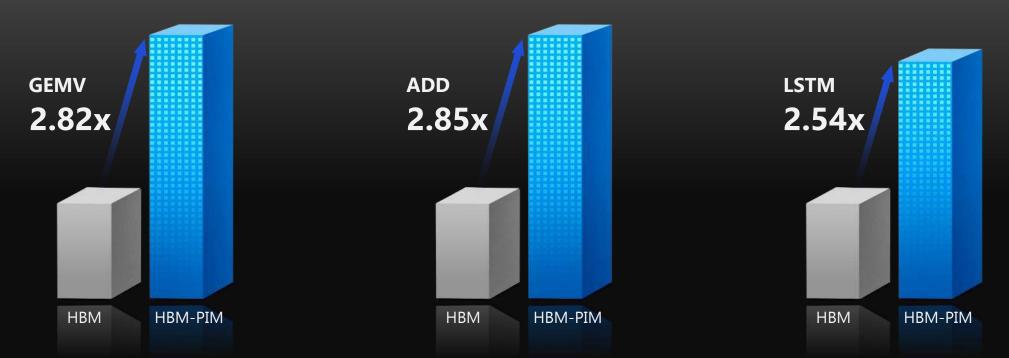

• Performance Gain: GEMV 2.82x, Add 2.85x, LSTM\* 2.54x

#### - GEMV: vector (1280) × matrix (1280 by 640) = vector (640)

- ADD: vector (64K) + vector (64K) = vector (64K)

- LSTM: input dimension (1024), hidden dimension (1024)

- Confirmed that our baseline/PIM-accelerated logics use maximum available bandwidth

#### **Relative Performance**

\* Long Short-term Memory Layer

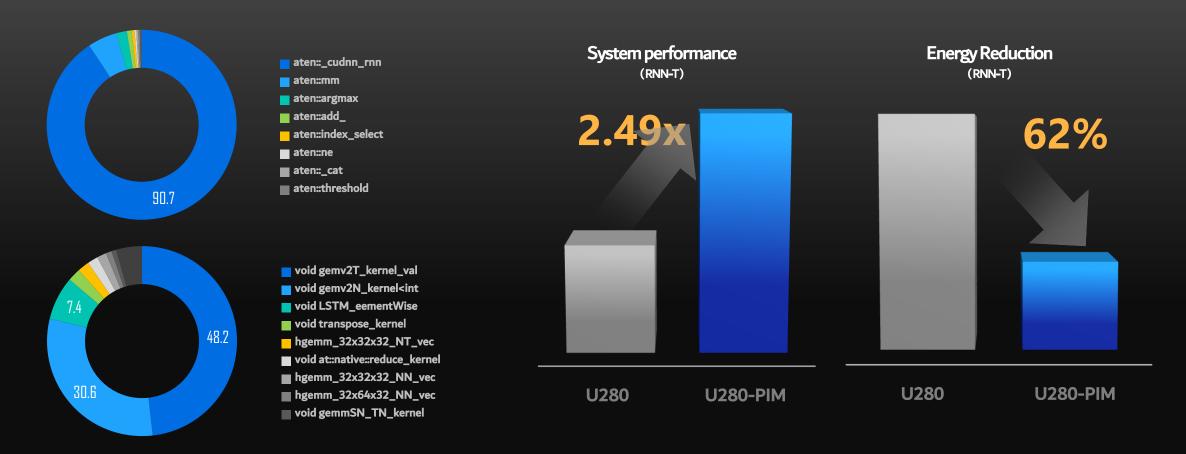

# Xilinx Alveo U280: RNN-T Performance and Energy Recurrent Neural Network Transducer

- LSTM layer consumes 90.7% of the running time, while vector-matrix multiplication kernel uses 78.8%. ٠

- PIM-enabled system reduces inference latency by 2.49X and the energy reduction by 62% ٠

# Expansion of PIM technology, LPDDR5-PIM

- Evaluated the performance and energy efficiency based on system-level simulation

- Assumption: 8.2TFLOPS and 2.5TFLOPS/W NPU, 1MB SRAM, FP16, No zero-skipping, 1-channel 12.8GB/s LPDDR5X-6400

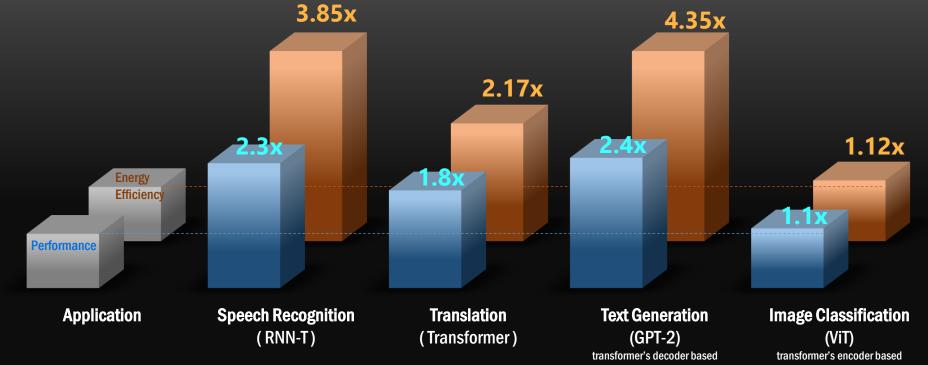

- Performance Gain: 2.3x (RNN-T speech recognition), 1.8x (transformer-based translation) and 2.4x (GPT-2 text generation)

SAMSUNG LPDDR5-PIM

• Energy Efficiency: 3.85x (RNN-T), 2.17x (transformer) and 4.35x (GPT-2)

### **Extensive evaluation for LPDDR5-PIM**

- Evaluated the performance and energy efficiency based on layer-by-layer analytical model — Assumption: 61TOPS and 5TOPS/W NPU, LLC 8MB (4MB is used), INT8, No zero-skipping, Only 20GB/s DRAM BW allocated for NPU

- Performance Gain: 2.1x (transformer-based speech recognition) and 1.2x (video bokeh)

- Energy Efficiency: 2.86x (transformer-based speech recognition) and 1.30x (video bokeh)

| Application                       |                         | Model                                 | Input     | PIM Target Operation | Performance | Energy Efficiency |

|-----------------------------------|-------------------------|---------------------------------------|-----------|----------------------|-------------|-------------------|

| Natural<br>Language<br>Processing | Speech Recognition      | Transformer                           | 10.1sec   | BLAS1,2              | 2.1x        | 2.86x             |

|                                   |                         | Listen-attend-spell                   | 10.1sec   | BLAS2                | 3.5x        | 8.33x             |

|                                   | Question & Answer       | BERT-Large                            | 512 words | BLAS1                | 1.8x        | 1.75x             |

|                                   |                         | ALBERT-Large                          | 512 words | BLAS1                | 1.7x        | 1.75x             |

|                                   | Machine Translation     | DeepSpeech2 + Transformer + Tacotron2 | 10sec     | BLAS2                | 3.5x        | 7.69x             |

| Computer<br>Vision                | Video Bokeh             | DeepLab V3+ (ResNet-101)              | 512x512   | BLAS1                | 1.2x        | 1.30x             |

|                                   |                         | DeepLab V3 (ResNet-50)                | FHD       | BLAS1                | 1.1x        | 1.02x             |

|                                   |                         |                                       | 4K        | BLAS1, 1x1 Conv      | 1.2x        | 1.08x             |

|                                   |                         |                                       | 8K        | BLAS1, 1x1 Conv      | 1.3x        | 1.16x             |

|                                   | Depth Estimate          | DORN                                  | 4K        | BLAS1                | 1.1x        | 1.10x             |

|                                   |                         |                                       | 8K        | BLAS1                | 1.2x        | 1.11x             |

|                                   | Image2Image translation | StarGAN                               | 8K        | BLAS1                | 1.1x        | 1.02x             |

# How can PIM guarantee deterministic latencies are essential to facilitate HBM-PIM with unmodified During AB(or AB-PIM) mode, the host processor can control execution of every PIM instruction one by one with its load (LD) and store (ST) instructions which are

**Executions of PIM instructions with** standard DRAM commands and

JEDEC-standard compliant DRAM

translated into standard DRAM

commands to DRAM

controllers

Is PIM technology compatible with RAS features?

For Aquabolt-XL, we disabled system ECC because the HBM device cannot generate system-specific ECC code for **PIM-generated data**

For the next generation of PIM-enabled HBM, we expect to deploy on-die ECC. In this architecture, PIM logic can share the ECC encode/decode circuitry, and data can be protected without incurring additional latency or throughput loss

Do application programmers need to JEDEC standard know how PIM works? compatibility?

No. Application programmers are able to run existing ML applications on a system using HBM-PIM without any changes to the source code, by using PIM-aware software stack. PIM software stack can detect PIM-beneficial operations and offload them to HBM-PIM without programmer awareness.

### **Frequently Asked Questions**

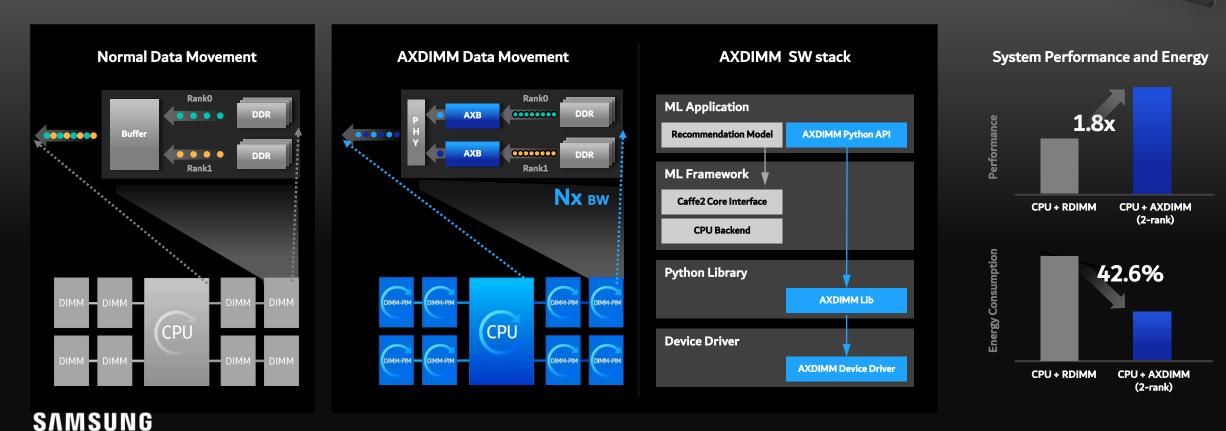

# AXDIMM, DIMM-PIM Concept

- CPU-memory data movement bottlenecks system performance → rank-level parallelism is needed

Samsung to provide AXDIMM SW stack to offload the acceleration functions in AXB(AXDIMM Buffer)

- Improve the performance and energy efficiency of the system with in-DIMM processing

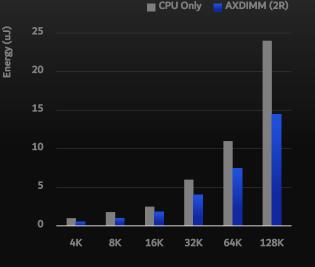

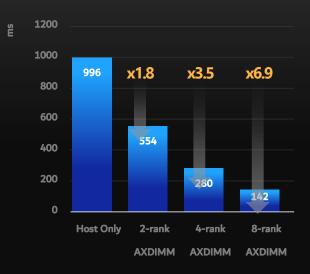

- Utilize up to higher in-DIMM bandwidth by multi-Rank parallel operation, 1.8x by 2-rank

- Reduce data movement energy by utilizing in-DIMM data processing unit, -42.6% by 2-rank

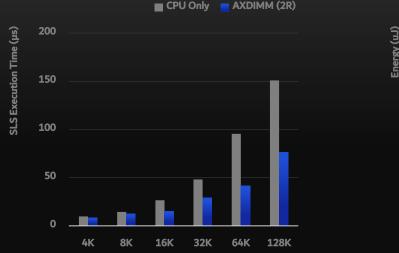

### **AXDIMM** evaluation system and results

- Setup x86 based AXDIMM platform with Xilinx Zynq Ultrascale+ FPGA Chip

- Enabled RecNMP\* logic

- Achieved 1.8x SLS execution speed-up from HW

- Modified DLRM\*\* application utilizing AXDIMM

- Achieved 1.8x/3.5x/6.9x QPS

#### Performance and Energy gain by data size

#### Total Execution time of DLRM for 700 Requests

Total Read Data Size (Byte, batch)

Total Read Data Size (Byte, batch)

\*: RecNMP - L. Ke et al., "RecNMP: Accelerating Personalized Recommendation with Near-Memory Processing," 2020 ACM/IEEE 47th Annual International Symposium on Computer Architecture (ISCA) \*\*: DLRM - M. Naumov et al, "Deep learning recommendation model for personalization and recommendation systems," arXiv preprint, 2019

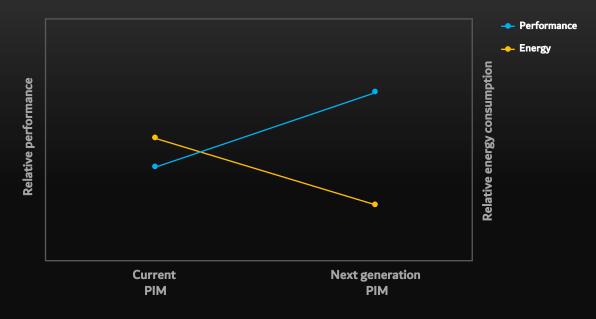

### **Future proposal**

- Wider target applications - PIM unit supporting multiple functions

- Various DRAM types - LPDDR5, DIMM-DDR5, GDDR6, HBM3

- New standards for PIM - Command truth table/timing for PIM

- Addendum or addition to current product specs, not new generations

- Enhanced performance

- Reduced energy

- Collaborate with industry - Supporting custom functions

#### Prospective PIM-supported data format

### Performance/Energy of next generation PIM

# Thank you